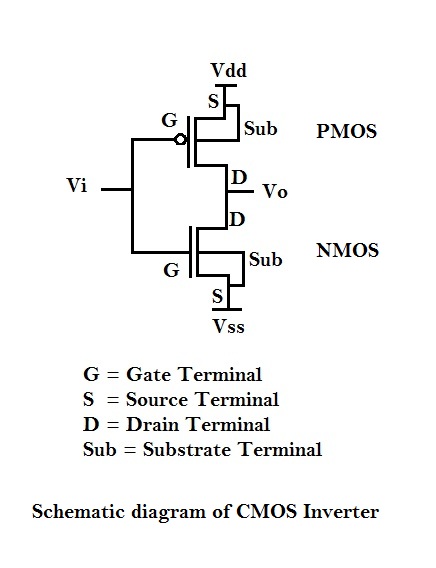

For best performance, use two transistors. Figure 5.1 shows the circuit diagram of a static CMOS inverter. If you need to source current, use a PNP and flip the design upside down. 3.1 Basic characterization of the CMOS inverter An inverter is the simplest logic gate which implement the logic operation of negation. This circuit can sink lots of current, but sourcing current requires a smaller resistor. There will be power dissipation in the resistor when 'driving high' (really a passive operation for this circuit), and current will flow through the resistor when you're driving low, so make the resistor as large as your load capacitance, switching speed, and input impedance allow. Ever圜ircuit user community has collaboratively. Real-time circuit simulation, interactivity, and dynamic visualization make it a must have application for professionals and academia.

#Cmos inverter logic simulator

Ever圜ircuit is an easy to use, highly interactive circuit simulator and schematic capture tool. When the input voltage is above $V_$ through the resistor. A CMOS inverter, as presented in ENGR 40M lecture on logic gates. This creates a simple inverter in a small space. You can also replace the top transistor with a resistor: Mason Lecture Notes .3 Transistor Switching Characteristics. With a logic-level PNP and NPN, you can make a push-pull totem-pole circuit that will have similar power requirements to an inverter IC. Example CMOS Logic Gate Synthesis.doc 1/6 Jim Stiles The Univ. CMOS logic circuit CMOS logic circuit V VDD logic 1 voltages logic 0 voltages undefined. However, if simplicity or education is your goal, you can do fairly well with a simple FET inverter. Historically, most CMOS gates, inverters, and high-current IC products were unbuffered and exhibited good logic-system performance, speed, noise immunity, and quasi-linear characteristics in a wide variety of applications. VOH: Nominal voltage corresponding to a high logic state at the output of a logic gate for vI VOL. of EECS For example, consider the CMOS inverter: For more complex digital CMOS gates (e.g., a 4-input OR gate), we find: 1) The PUN will consist of multiple inputs, therefore requires a circuit with multiple PMOS transistors. You'll never beat an IC for size with discrete components tcrosley's link only draws a few ♚ and the footprint is a SOT23-5, which is only 2.1x2.4mm. CMOS Device Structure.doc 4/4 Jim Stiles The Univ.

0 kommentar(er)

0 kommentar(er)